计算机三级(嵌入式系统开发技术)机试模拟试卷354

选择题

1.数字信号处理器在嵌入式系统中得到广泛使用,下面关于数字信号处理器的叙述中错误的是( )。(C)

A. 它的英文缩写是DSP

B. 它比通用的微处理器能更好地满足高速数字信号处理的要求

C. 它特别适合于文字处理和图形用户界面

D. 手机和数码相机等产品通常都含有数字信号处理器

解析:数字信号处理器(DSP)是一种专用于数字信号处理的微处理器,它对通用处理器的逻辑结构和指令系统进行了优化设计,使之能更好地满足高速数字信号处理的要求,特别适合音频、视频等数字信号的数据处理效率,手机和数码相机等产品通常都含有数字信号处理器。故本题选择C。

2.片上系统(SoC)也称为系统级芯片,下面关于SoC叙述中正确的是( )。(B)

A. SoC芯片中只有一个CPU或DSP

B. SoC已经成为嵌入式处理芯片的主流发展趋势

C. SoC是集成电路加工工艺进入纳米时代后的产物

D. 片上系统使用单个芯片进行数据的采集、转换、存储和处理,它不支持I/O功能

解析:片上系统(或系统级芯片)即SOC或SoC,是目前广泛使用的一种嵌入式处理芯片,它是电子设计自动化(EDA)水平提高和大规模集成电路制造技术(VLSI)发展的成果,芯片中既包含处理器又包含存储器及外围电路,单个芯片就能实现数据的采集、转换、存储、处理和I/O等多种功能,目前大多数32位的嵌入式处理芯片均为SOC,包括智能手机和平板电脑,其逐渐成为集成电路设计的主流发展趋势。故本题选择B。

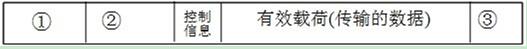

3.计算机局域网传输数据时,必须把数据组织成规定格式的“帧”,每数据帧由下图所示的5个部分组成,其中①、②、③分别是( )。

(A)

(A)

A. 发送设备MAC地址、接收设备MAC地址、校验信息

B. 发送设备MAC地址、校验信息、接收设备MAC地址

C. 校验信息发送设备MAC地址、接收设备MAC地址

D. 接收设备MAC地址、发送设备MAC地址、校验信息

解析:局域网采用分组交换技术,发送设备必须把要传输的数据分成小块,即帧,一次只能传输帧。数据帧中除了包含需要传输的数据(称之为“有效载荷”)之外,还必须包含发送该数据帧的发送设备地址和接收该数据帧的接收设备地址。另外数据帧中还需要附加一些信息随同数据起进行传输,包括控制信息和校验信息,以供接收设备在收到数据之后验证数据传输是否正确。这些信息包括控制信息和校验信息。故本题选择A。

4.通常嵌入式系统对实时性和可靠性都有一定要求,如果把ATM柜员机和数码相机两者进行比较,它们中对实时性和可靠性要求较高的分别是( )。(B)

A. ATM柜员机、数码相机

B. 数码相机、ATM柜员机

C. ATM柜员机、ATM柜员机

D. 数码相机、数码相机

解析:嵌入式系统按实时性要求可分为非实时系统,软实时系统和硬实时系统。选项中对实时性要求较高的是数码相机,对可靠性要求较高的是ATM柜员机。故本题选择B。

5.关于处理器内核说法正确的是( )。(C)

A. 51内核是RISC指令集结构

B. AVR内核是CISC指令集结构

C. MSP430内核采用冯·诺依曼结构

D. 所有ARM内核均采用哈佛结构

解析:嵌入式处理器的体系结构按指令集可分为两大类:复杂指令集结构(CISC)及精简指令集结构(RISC);按存储机制分为冯·诺依曼结构及哈佛结构;按不同内核系列可分为51、AVR、MSP430、MIPS、PowerPC、MC68K、ARM等。其中,PowerPC、MC68K、MIPS采用RISC、哈佛结构,ARM也采用RISC,多数为哈佛结构。故本题选择C。

6.关于ARMCortex-M处理器的特点,以下说法错误的是( )。(D)

A. 功能强

B. 耗电少

C. RISC结构

D. 多周期操作

解析:Cortex-M系列是面向微控制器的处理器核,极高性价比、最低成本、极低功耗;具有处理速度快、代码密度高、软件可移植性好的特点。故本题选择D。

7.以下ARM处理器,只有Thumb-2状态和调试状态的是( )。(D)

A. ARM7

B. ARM9

C. ARM11

D. ARMCortex-M3

解析:在ARM的体系结构中,处理器可以工作在3种不同的状态:①ARM状态②Thumb状态及Thumb-2状态③调试状态。其中,除支持Thumb-2的ARM处理器外,其他所有ARM处理器都可以工作在ARM状态,而Cortex-M3只有Thumb-2状态和调试状态。故本题选择D。

8.已知内存单元0000000~0000000以小端模式存放一个32位数据0x32303134,R1=0000000,R0=0,执行ARM指令LDRHR0,[R1]之后,R0的值为( )。(C)

A. 0x32303134

B. 0x0003230

C. 0x00003134

D. 00000032

解析:所谓小端模式,是指数据字的高位保存在内存的高地址中,而数据字的低位保存在内存的低地址;指令LDRHR0,[R1]是寄存器间接寻址,将R1的内容形成操作数的有效地址,从中取得半字数据存入寄存器R0中。故本题选择C。

9.已知R1=8,R0=9,执行指令MOVR0,R1,LSR#3后,R0的值为( )。(A)

A. 1

B. 8

C. 0x10

D. 0x80

解析:题中指令为将R1逻辑右移3位之后存到R0中,左端用0来补充。故本题选择A。

10.对于ARM处理器以下不属于逻辑运算指令助记符的是( )。(D)

A. AND

B. BIC

C. EOR

D. SBC

解析:ARM指令集中,SBC是带借位减法指令,是算术运算指令,不属于逻辑运算助记符。故本题选择D。

11.关于ARM处理器的工作模式,以下说法错误的是( )。(B)

A. 用户模式是程序正常执行的工作模式

B. 管理模式负责处理存储器故障,实现虚拟存储器和存储器的保护

C. 系统模式运行特权级的操作系统任务

D. 当处理器处于用户模式时,如果没有异常发生是不能改变工作模式的

解析:ARM体系结构支持7种工作模式,取决于当前程序状态寄存器CPSR的低5位值。用户模式是程序正常执行工作模式,当处理器处于用户模式时,如果没有异常发生不能改变工作模式;系统模式运行特权级的操作系统任务;管理模式是操作系统的保护模式,处理软中断。故本题选择B。

12.以下关于ARM状态寄存器CPSR的说法正确的是( )。(D)

A. CPSR决定存储器的数据类型和存储模式

B. CPSR中I为快速中断禁止控制位

C. CSPR中的T为陷井标志

D. CPSR决定ARM处理器工作模式

解析:CPSR为当前程序状态寄存器,决定ARM处理器工作模式。N为符号标志,N=1表示运算结果为负数,N=0表示运算结果为正数;F为禁止快速中断FIQ的控制位,F=0允许FIQ中断;V为溢出

本文档预览:3600字符,共22212字符,源文件无水印,下载后包含无答案版和有答案版,查看完整word版点下载