计算机三级嵌入式系统开发技术(嵌入式系统硬件组成)模拟试卷5

选择题

1.下面关于嵌入式最小硬件系统的叙述中,错误的是( )。(D)

A. 可使用LDO为嵌入式最小系统供电,LD0是指低压差稳压器

B. 时钟电路为嵌入式最小系统中的嵌入式处理器提供工作时需要的时钟信号

C. 如果处理器内嵌的存储器能满足嵌入式最小系统的应用需要,则系统无需扩展外部存储器

D. 嵌入式最小系统包括复位电路,嵌入式处理器的复位引脚为nRESET时,表示高电平复位

解析:提供嵌入式处理器运行必备条件的硬件电路与嵌入式处理器共同构成嵌入式最小硬件系统,可使用LDO为嵌入式最小系统供电,LDO是指低压差稳压器;时钟电路为嵌入式最小系统的嵌入式处理器提供工作时需要时钟信号;如果处理器内嵌Flash程序存储器容量足够,则无需护展外部存储器;嵌入式最小系统包括复位电路,嵌入式处理器的复位引脚为nRESET时,表示低电平复位。故本题选择D。

2.下面与嵌入式处理器复位相关的叙述中,错误的是( )。(A)

A. 嵌入式处理器都有一个系统复位引脚为nRESET或RESET,nRESET表示高电平复位

B. 嵌入式系统常使用外接复位芯片提供的复位信号来实现系统的可靠复位

C. 有些微处理器用复位芯片可通过两个不同引脚分别输出高电平或低电平有效的复位信号

D. ARM复位后PC指针指向某个唯一的地址

解析:嵌入式处理器都有一个系统复位引脚为nRESET或RESET,n表示低电平复位,不带n的表示高电平复位。本题答案为A选项。

3.下面关于嵌入式系统中复位电路的叙述中,错误的是( )。(B)

A. 复位电路是嵌入式最小硬件系统的一个组成部分

B. 嵌入式处理器系统复位引脚为nRESET时,表示高电平复位

C. 一般情况下,复位信号的时间宽度必须保持若干个处理器时钟周期才能使系统可靠复位

D. 对于经典ARM处理器复位后,PC指针指向唯一的地址0000000

解析:复位电路是嵌入式最小硬件系统的一个组成部分,嵌入式处理器系统复位引脚为nRESET时,表示低电平复位(不带的表示高电平复位),一般情况下,复位信号的时间宽度必须保持若千个处理器时钟周期才能使系统可靠复位,对于经典ARM处理器复位后,PC指针指向唯一的地址0000000故此题选择B。

4.下面是关于嵌入式系统中电源电路的叙述,其中错误的是( )。(C)

A. 应按照嵌入式硬件系統需要的最大功率确定嵌入式系统中电源电路的输出功率

B. 嵌入式系统中电源电路的输入如果为交流电,则-般需要采用AC-DC模块

C. 78xx系列是一种AC-DC模块

D. 设计嵌入式系统的电源电路时应考虑电磁兼容性问题

解析:应按照嵌入式硬件系统需要的最大功率确定嵌入式系统中电源电路的输出功率;嵌入式系统中电源电路的输入如果为交流电,则-般需要采用AC-DC模块;设计嵌入式系统的电源电路时应考虑电磁兼容性问题;C选项中,78xx是稳压器的系列名称。本题答案为C选项。

5.下面是关于AMBA总线的叙述:

Ⅰ.按照AMBA规范,以ARM内核为基础的嵌入式处理芯片采用系统总线与外围总线的层次结构构建片上系统

Ⅱ.AMBA的系统总线主要用于连接高带宽快速组件

Ⅲ.AMBA的外围总线主要连接低带宽组件以及与外部相连的硬件组件

Ⅳ.系统总线通过桥接器与外围总线互连

上述叙述中,正确的是( )。(D)

A. 仅Ⅰ

B. 仅Ⅰ和Ⅱ

C. 仅Ⅰ、Ⅱ和Ⅲ

D. 全部

解析:按照AMBA规范,以ARM内核为基础的嵌入式处理芯片采用系统总线与外围总线的层次结构构建片上系统。AMBA的系统总线主要用于连接高带宽快速组件。AMBA的外围总线主要连接低带宽组件以及与外部相连的硬件组件。系统总线通过桥接器与外围总线互连。全部选项正确,故本题选择D。

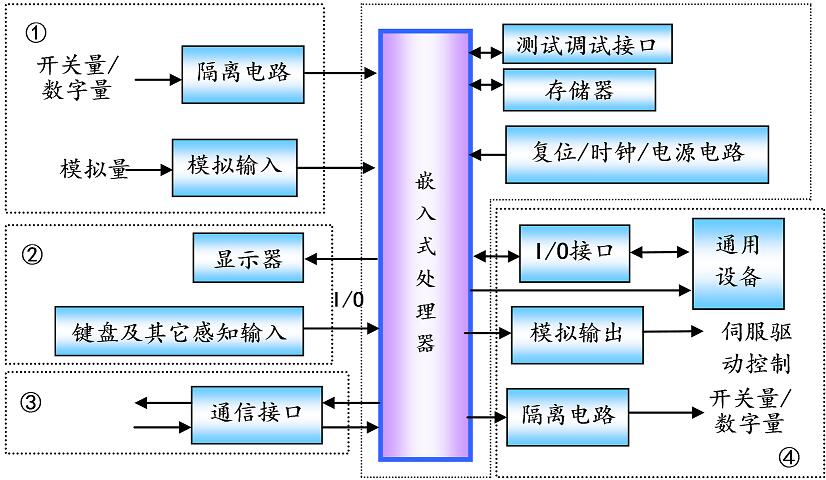

6.下图为典型嵌入式系统硬件组成原理图,图中①、②、③、④这四个部分分别为( )。

(B)

(B)

A. 相互互连通道、前向通道、后向通道、人机交互通道

B. 前向通道、人机交互通道、相互互连通道、后向通道

C. 后向通道、人机交互通道、相互互连通道、前向通道

D. 人机交互通道、相互互连通道、后向通道、前向通道

解析:典型嵌入式系统硬件由嵌入式最小硬件系统、前向通道、人机交互通道、相互互连通道、后向通道组成。故此题选择B。

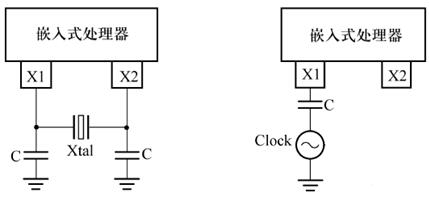

7.下图为典型的嵌入式处理器时钟电路设计方法,下面是结合该图的相关叙述,其中错误的是( )。

(D)

(D)

A. 左图中的Xtal为晶体振荡器

B. 右图中的Clock应采用稳定的时钟信号源

C. 左图中的时钟电路设计方法使用了嵌入式处理器内置的时钟信号发生器

D. 设计嵌入式处理器的时钟电路时,选择的Xtal的频率或者Clock的频率必须保证嵌入式处理器能工作在最高工作频率

解析:在设计嵌入式处理器的时钟电路时,选择的晶振或定时器的频率只要满足需求即可,不一定必须保证嵌入式处理器能工作在最高工作频率。本题答案为D选项。

8.下面是关于嵌入式系统使用的存储器的叙述,其中错误的是( )。(C)

A. 嵌入式系统使用的存储器以半导体存储器为主

B. 铁电存储器(FRAM)在嵌入式系统已得到应用

C. 静态存储器SRAM是非易失性存储器

D. 动态存储器DRAM是易失性存储器

解析:随机存取存储器包括静态和动态两种形式,即SRAM和DRAM,它们都是易失性存储器,即掉电后信息丢失。C选项错误,故本题选择C。

9.下面是关于ARM处理器中模拟通道组件的叙述,其中错误的是( )。(D)

A. 利用ARM处理器内嵌的ADC可完成从模拟信号到数字信号的变换

B. 利用ARM处理器内嵌的DAC可完成从数字信号到模拟信号的变换

C. 有些ARM处理器内部的模拟组件除包括ADC和DAC外,还包含比较器等

D. ARM处理器内嵌的ADC的AD转换精度与ADC的位数无关

解析:有些ARM处理器内部的模拟组件除包括ADC和DAC外,还包含比较器;ADC和DAC可以分别完成模拟信号到数字信号的变换和数字信号到模拟信号的变换,其转换精度与位数正相关。故D选项错误。

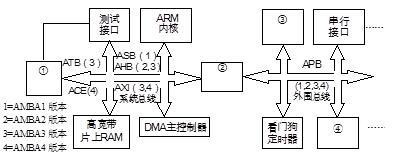

10.基于AMBA的典型ARM片上系统示意图如下图所示,图中①、②、③、④处可以是:

(C)

(C)

A. 并行接口、高带宽外部存储器控制接口、通用定时器、桥接器

B. 桥接器、并行接口、高带宽外部存储器控制接口、通用定时器

C. 高带宽外部存储器控制接口、桥接器、并行接口、通用定时器

D. 通用定时器、并行接口、高带宽外部存储器控制接口、桥接器

解析:根据典型ARM片上系统结构图,①处为高带宽外部存储器控制接口、②桥接器、③并行接口以及④为通

本文档预览:3600字符,共11571字符,源文件无水印,下载后包含无答案版和有答案版,查看完整word版点下载