嵌入式系统设计师上午基础知识考试选择题专项强化真题试卷6

中文选择题

1.若内存按字节编址,用存储容量为32K×8比特的存储器芯片构成地址编号 A0000H~DFFFFH的内存空间,则至少需要(1)片。(C)

A. 4

B. 6

C. 8

D. 10

解析:本题考查内存容量的计算。给定起、止地址码的内存容量=终止地址-起始地址+1。将终止地址加1等于E0000H,再减去起始地址,即E0000H-A0000H=40000H。十六进制的(40000)16=218。组成内存储器的芯片数量=内存储器的容量/单个芯片的容量。218/(32*210)=218/215=23

2.在FAT16文件系统中,若每个簇(cluster)的大小是2KB,那么它所能表示的最大磁盘分区容量为(53)。(D)

A. 2MB

B. 32MB

C. 64MB

D. 128MB

解析:在FAT16文件系统中,FAT表项的最大个数为2的16次方,而每个簇的大小为2KB,因此它所能表示的最大磁盘分区容量为216*2KB=128MB。

3.逻辑表达式求值时常采用短路计算方式。“&&”“||”“!”分别表示逻辑与、或、非运算,“&&”“||”为左结合,“!”为右结合,优先级从高到低为“!”“&&”“||”。对逻辑表达式“x&&(y ||!z)”进行短路计算方式求值时,_______。(B)

A. x为真,则整个表达式的值即为真,不需要计算y和z的值

B. x为假,则整个表达式的值即为假,不需要计算y和z的值

C. x为真,再根据z的值决定是否需要计算y的值

D. x为假,再根据y的值决定是否需要计算z的值

解析:本题考查逻辑运算知识。

由“逻辑与”“逻辑或”运算构造的逻辑表达式可采用短路计算的方式求值。

“逻辑与”运算“&&”的短路运算逻辑为:a&&b为真当且仅当a和b都为真,当a为假,无论b的值为真还是假,该表达式的值即为假,也就是说此时不需要再计算b的值。

“逻辑或”运算“||”的短路运算逻辑为:a||b为假当且仅当a和b都为假,当a为真,无论b的值为真还是假,该表达式的值即为真,也就是说此时不需要再计算b的值。

对逻辑表达式“x&&(y ||!z)”进行短路计算方式求值时,x为假则整个表达式的值即为假,不需要计算y和z的值。若x的值为真,则再根据y的值决定是否需要计算z的值,y为真就不需要计算z的值,y为假则需要计算z的值。

4.分配到必要的资源并获得处理机时的进程状态是_______。(B)

A. 就绪状态

B. 执行状态

C. 阻塞状态

D. 撤销状态

解析:本题考查嵌入式操作系统的基础知识。

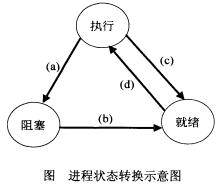

嵌入式操作系统中的进程状态有三种:执行状态(运行状态)、就绪状态和阻塞状态(等待状态),三种状态的定义如下:

就绪状态:进程已获得了除处理机以外的所有资源,一旦获得处理机就可以立即执行,此时进程所处的状态为就绪状态。

执行状态(运行状态):执行状态又称为运行状态,当一个进程获得必要的资源并正在处理机上执行时,该进程所处的状态为执行状态。

阻塞状态(等待状态):阻塞状态又称等待状态,睡眠状态。正在执行的进程,由于发生某事件而暂时无法执行下去(如等待输入/输出),此时进程所处的状态为阻塞状态。处于阻塞状态的进程尚不具备运行条件,这时即使处理机空闲,它也无法使用。

根据本题的题意,进程已分配到所需资源并获得处理机,此时进程应进入执行状态。故本题的正确答案为B。

5.软件需求分析阶段的测试手段一般采用______。(C)

A. 总结

B. 阶段性报告

C. 需求分析评审

D. 黑盒测试

解析:本题考查软件生命周期阶段和软件测试验证的基础知识。

根据软件生命周期经典模型“瀑布模型”中的定义,软件需求分析阶段是对软件的功能要求进行分解,该阶段的输出的工作产品一般是《软件需求规格说明》。

而对软件阶段工作产品的验证的手段一般分为评审、测试、分析,对于需求分析阶段产生的《软件需求规格说明》来说,一般是开展相应的评审活动去验证需求的完整性、正确性和一致性。

故本题应选择C。

6.以下关于嵌入式系统时钟管理的叙述中,错误的是_____________。(C)

A. 系统的主时钟可以由外部时钟源提供,也可由外部晶体振荡器提供

B. 时钟控制逻辑可以在不需要锁相环的情况下产生慢速时钟

C. 利用锁相环可以对输入时钟进行倍频输出,但无法改变输出时钟的相位

D. 可以通过软件来控制时钟与每个外围模块的连接还是断开

解析:本题考查嵌入式系统时钟管理方面的基础知识。

嵌入式系统主时钟可以由外部时钟源提供,也可以由外部振荡器提供。时钟控制逻辑可以在不需要锁相环(Phase Locked Loops,PLL)的情况下产生慢速时钟,并且可以通过软件来控制时钟与每个外围模块是连接还是断开,从而降低功耗。系统时钟源直接采用外部晶振时,内部PLL电路可以调整系统时钟,使系统运行速度更快。由于片内的PLL电路可以兼具频率放大和信号提纯的功能,因此,系统可以以较低的外部时钟信号获得较高的工作频率,从而降低因高速开关时钟所造成的高频噪声。锁相环在工作的过程中,当输出信号的频率与输入信号的频率相等时,输出电压与输入电压保持固定的相位差值,即输出电压与输入电压的相位被锁住。

7.以下关于软件验证的叙述中,错误的是_____________。(D)

A. 试图证明在软件生命周期各阶段,软件产品或中间产品能满足客户需求

B. 强调对于过程的检验,而不是对于结果的检验

C. 验证软件是否满足它的需求规格说明

D. 验证软件的手段只有软件测试和评审

解析:本题考查关于软件验证方面的概念和知识。

软件验证,就是希望证明在软件生命周期各阶段,软件产品或中间产品能满足客户需求,强调对于过程的检验,而不是对于结果的检验,验证软件是否满足它的需求规格说明。

验证软件的手段有测试、同行评审、审查、走查、模拟、演示等。

8.某个应用任务TaskA正在等待信号量到来从而执行,此时TaskA所处的状态名称为_____________。(C)

A. 就绪态状态

B. 执行状态

C. 阻塞状态

D. 结束状态

解析: 本题考查嵌入式操作系统的基础知识。

操作系统中的进程状态有三种:执行状态、就绪状态和阻塞状态。下图给出了进程三个状态:运行、就绪、等待之间的切换关系。

9.

执行下面的一段C程序后,变量ret的值为_____________。

char str[20];

int ret=strlen(strcpy(str,’’Hello_World’’));(B)

A. 0

B. 11

C. 12

D. 20

解析:本题考查C语言基础知识。

本文档预览:3600字符,共10569字符,源文件无水印,下载后包含无答案版和有答案版,查看完整word版点下载